本篇目录:

issim仿真如何输出十进制时序

在ISSIM的设计界面中,选择输出时序的电路元件,如时钟、触发器、计数器等,并将其连接起来。

要看交通灯的时序仿真,您可以按照以下步骤进行:确定仿真软件:选择一款交通仿真软件,例如SUMO(SimulationofUrbanMObility)、VISSIM(TrafficMicrosimulation)等。这些软件可以模拟交通流动和交通信号控制。

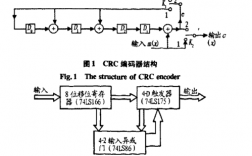

该程序实现的功能:设计一个至少4位的十进制计数器,具有加减计数功能和置数功能,并能通过数码管显示计数结果。减数为零时发声报警。

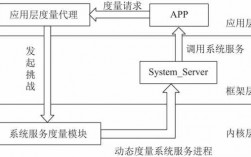

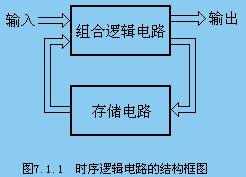

利用Verilog HDL语言自顶向下的设计方法设计交通灯控制系统,使其实现道路交通的正常运转,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过Xilinx ISE02和ModelSim 6完成综合、仿真。

简述用QuartusⅡ开发数字系统的过程

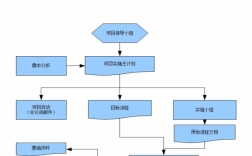

双击打开QuartusII软件,选择 file---New Project Wizard...弹出如下窗口,本窗口介绍创建一个工程需要执行的设置,点击next。

而可编程器件的广泛应用,为数字系统的设计带来了极大的灵活性。由于可编程器件可以通过软件编程对硬件的结构和工作方式进行重构,使得硬件的设计可以如同软件设计那样快捷方便。

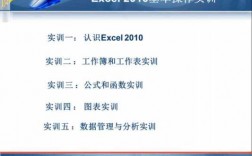

工程建立2 2 原理图的输入5 3 文本编辑 (verilog)15 4 波形仿真16 Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1所示。

拓展:MAX+plus Ⅱ和Quartus Ⅱ是Altera公司提供的可编程逻辑器件感叹具,理解并掌握它们就可以利用Altera公司的可编程逻辑器件开发出符合要求的数字系统。

FPGA设计中的仿真有哪三种

包括以下三种:RTL级行为仿真:在综合和实现前便可验证设计,用来检查代码语法和验证代码像设计者想要的功能一样工作,早期的行为级仿真可以尽早发现问题。综合后仿真:使用综合网表仿真,验证综合后设计满足功能需求。

功能仿真 ( 前仿真 )功能仿真是指在一个设计中, 在设计实现前对所创建的逻辑进行的验证其功能是否正确的过程。

FPGA 厂家自带的编程环境里有仿真的工具,如altera的quartus ,或者用multisim 等第三方的仿真软件。

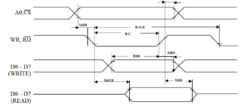

如何用proteus仿真出8086的总线周期时序图

1、T1,cpu往多路服用总线上发出地址信息,指出要寻址的存储单元T2,cpu从总线上撤消地址,使总线的低16位浮置成高阻态,为传输数据做准备。总线最高4位(A19~A16)用来输出本总线周期状态信息。

2、标号也是用LBL工具,在总线支线上要连接的两端支线上标上同一标号。如果有连续标注,可以用快捷方法。

3、Proteus中有仿真8086CPU例子,在C盘的这个文件夹下:C:\Program Files\Labcenter Electronics\Proteus 7 Professional\SAMPLES\VSM for 8086\8086 Demo Board 画仿真图,然后写程序,要生成EXE可执行文件。

到此,以上就是小编对于时序仿真的基本步骤的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏